2. Alat dan Bahan

[Kembali]

a. Jumper

b. Panel DL 2203D

3. Rangkaian Simulasi [Kembali]

4. Prinsip Kerja Rangkaian

[Kembali]

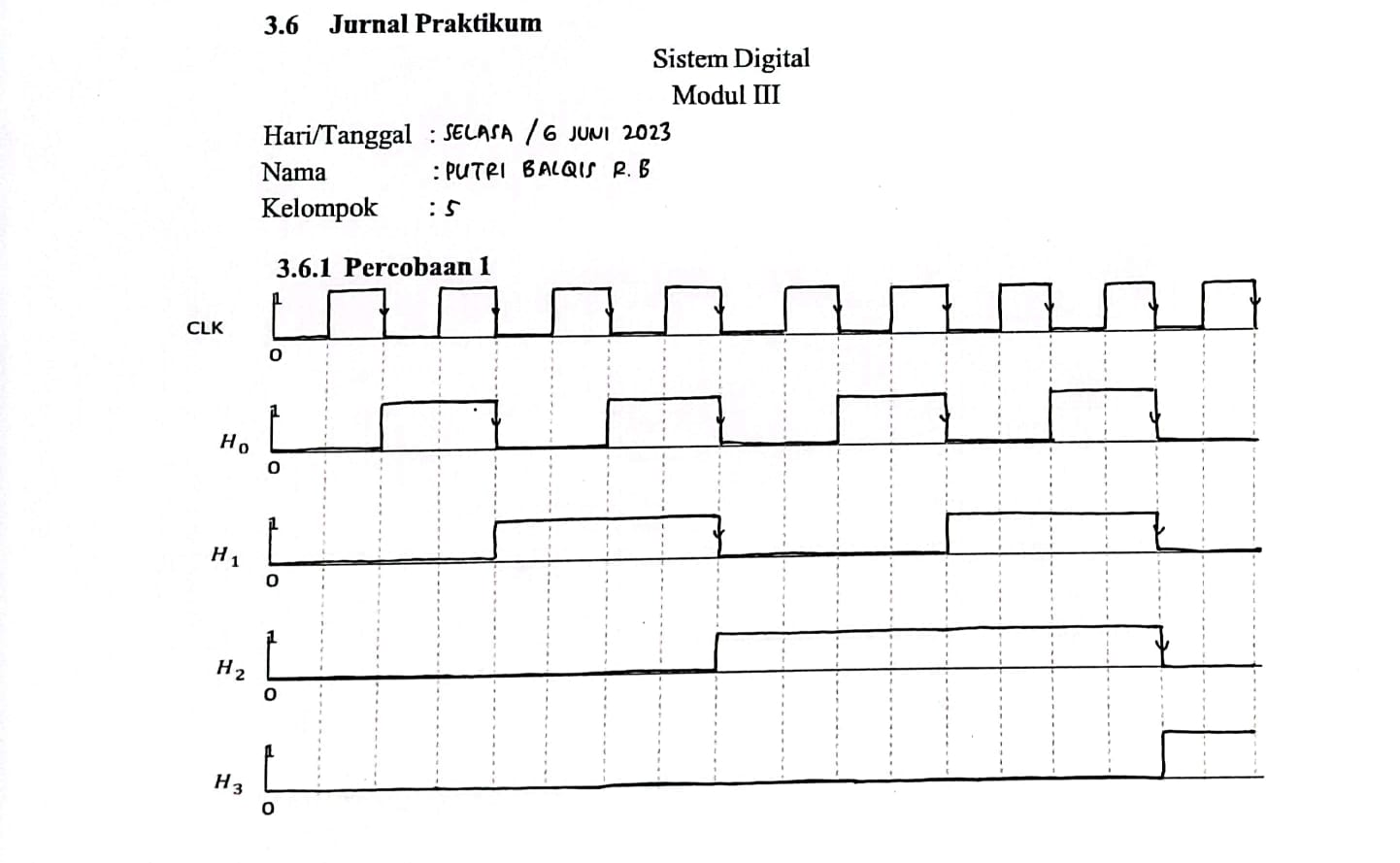

Prinsip kerja percobaan 1 Asynchronous Binary Counter dengan IC J-K Flip flop yaitu saat input T- flip flop (input J dan K disatukan) pada JK flip flop dihubung power, maka output IC akan mengalami kondisi toogle. Tetapi, karena lC JK flip flop memiliki input clock, dan dihubungkan ke clock juga maka Output toogle pada masing-masing IC akan berubah sesuai dengan keadaan aktifnya, dimana ia akan aktif saat fall time (kondisi aktif low).

Pada clock percobaan 1, clock hanya dihubungkan pada JK Flip flop pertama yang bertindak sebagai input, sehingga saat T Flip-plop dihubung power dimana dia bersifat rise time, maka untuk output yang dihasilkan pada JK Flip Flop adalah mulai dari nol. Ini juga berlaku pada JK flip flop kedua sampai Keempat, dimana untuk output yang dihasilkan dimulai dari 0 (tetap 0). Dengan demikian, dapat disimpulkan bahwa pada awalnya untuk output percobaan dimulai dari nol.

Saat Clock dalam kondisi fall time, maka output JK flip Flop pertama akan berubah dan naik bilangan binernya ke 1, sedangkan pada JK Flip flop kedua tidak terpengaruh apapun karena input clock IC kedua diperoleh dari output JK flip flop pertama sehingga clock IC kedua dalam kondisi rise time sehingga output IC kedua berlogika 0, begitupun seterusnya pada IC ketiga dan ke empat dimana untuk inputnya sendiri dalam kondisi rise time, sehingga diperoleh outputnya secara bergiliran dan bergantian mengalami kenaikan atau penurunan pada bilangan binernya, yang bergantung pada flip flopnya.

5. Video Rangkaian

[Kembali]

6. Analisa

[Kembali]

1. Analisa apa yang terjadi jika masing-masing input flip-flop selanjutnya dihubungkan dengan Q' flip-flop sebelumnya.

Jawab:

apabila masing-masing input flip-flop selanjutnya dihubungkan ke Q' flip-flop sebelumnya, maka rangkaian akan melakukan count down untuk outputnya dari F sampai 0.

2. Jelaskan perbedaan pemasangan rangkaian asynchronous counter up dengan asynchronous counter down.

Jawab:

rangakaian asynchronous counter up pada percobaan 1 terjadi apabila masing-masing input flip-flop selanjutnya dihubungkan dengan Q (output) flip-flop sebelumnya, sedangkan asynchronous counter down dirangkai dengan tiap-tiap input flip-flop selanjutnya disambungkan dengan Q' flip-flop sebelumnya.

3. Jelaskan apa yang terjadi saat rangkaian berjalan kaki S diaktifkan/input kaki S diberi logika 0.

Jawab:

saat kaki S berlogika 0 maka semua output pada rangkaian akan berlogika 1 karena set nya aktif, maka JK yang terhubung parallel akan mendapatkan kondisi set secara bersamaan dan output akan dipaksa menjadi 1111.

7. Link Download

[Kembali]

- Download HTML [klik disini]

- Donwload Rangkaian Simulasi [klik disini]

- Download Video Simulasi [klik disni]

- Download Datasheet ic 74LS112A [klik disini]

- Download Datasheet LED [klik disini]

Tidak ada komentar:

Posting Komentar