2. Alat dan Bahan

[Kembali]

a. Jumper

b. Panel DL 2203D

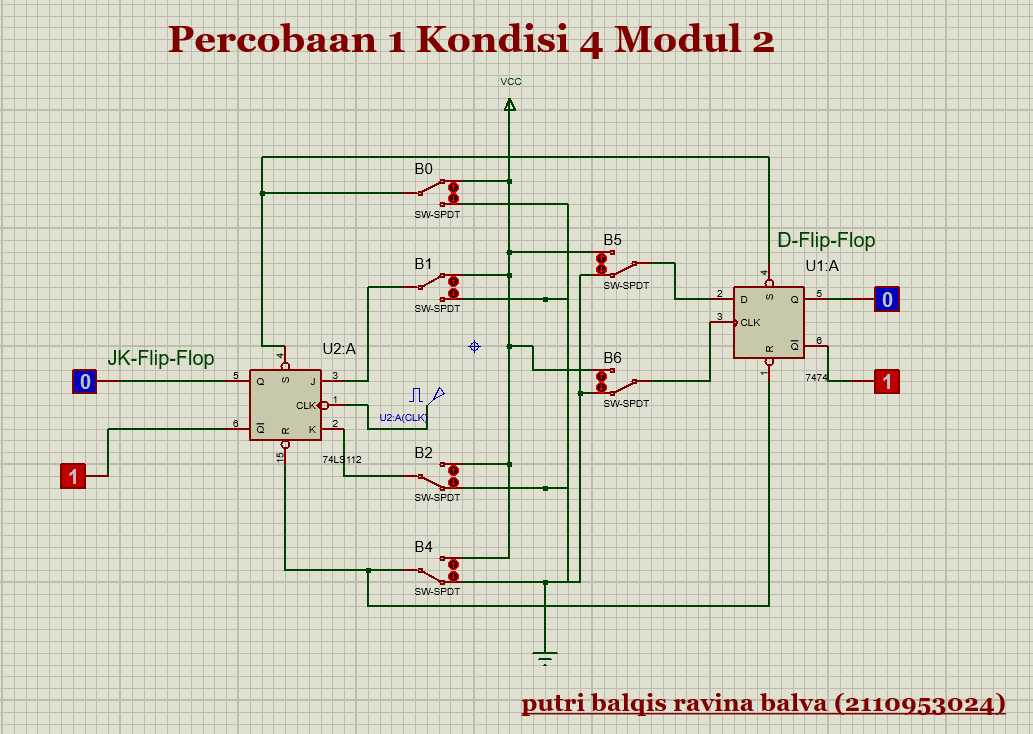

3. Rangkaian Simulasi [Kembali]

4. Prinsip Kerja Rangkaian

[Kembali]

Dapat kita lihat pada rangkaian, kita menggunakan JK flip-flop dan D flip-flop, JK flip-flop merupakan jenis flip flop yang dibangun dari R-S flip flop yang tidak memiliki kondisi terlarang pada rangkaiannya, J-K fllipflop memiliki 3 kaki input selain kaki S dan R, yaitu J, K, dan CLK (active low). D flipflop memiliki 2 kaki input selain kaki S dan R, yaitu D dan CLK. Dimana CLK akan menjadi penentu perubahan output terhadap input D yang diberikan dan CLK (active high). daninputnya adalah switch dengan 7 saklar yang diberi nama B0 – B6 yang dihubungkan dengan VCC. Prinsip kerja rangkaian ini yaitu dengan memvariasikan input dari flip flop dengan mengganti-ganti 7 switch, apakah ONatau OFF. Sesuai dengan tabel kebenarannya maka output dari masing masing flip flop akan bervariasi juga.

Contoh pada percobaan ke-1 variasi ke-1 dengan kondisi B0(R)=0, B1(S)=1, B2(J)=don't care, B3(CLK)=don't care, B4(K)=don't care, B5(D)=don't care, dan B6(CLK)=don't care didapat output pada JK flip-flop Q=0 dan Q'=1 dan D flip-flop Q=0 dan Q'=1. Hal ini dikarenakan karena nilai pada input kaki RS tidak sama sehingga RS flip-flop yang aktif sedangkan D flip-flop dan JK-flip-flop tidak aktif sehingga output yang keluar sesuai tabel kebenaran RS flip-flop Q=0 dan Q'=1 .

5. Video Rangkaian

[Kembali]

6. Analisa

[Kembali]

1. Analisa apa yang terjadi saat input B3 dan B2 dihubungkan ke clock dan K berlogika 1, gambarkan timing diagramnya

Jawab:

apabila rangkaian diatur input B3 dan B2 nya ke clock maka output pada Q akan berlogika 0 dan pada Q' berlogika 1, apabila komponen rangkaian R, S, dan J nya berlogika 1.

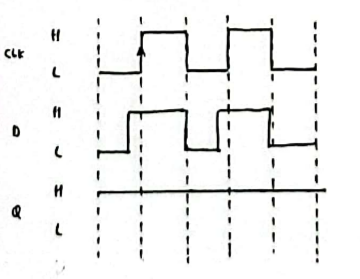

2. Analisa apa yang terjadi saat B5 dan B6 dihubungkan ke clock dan gambarkan timing diagramnya

Jawab:

apabila rangkaian percobaan 1 B5 dan B6 nya dihubungkan ke clock maka output Q pasti berlogika 1 karena input pada D akan berlogika 1/aktif apabila clock juga berlogika 1 dan output Q = tidak berubah jika clock = 0 (OFF)

7. Link Download

[Kembali]

- Download HTML [klik disini]

- Donwload Rangkaian Simulasi [klik disini]

- Download Video Simulasi [klik disni]

- Download Datasheet ic 74LS112A [klik disini]

- Download Datasheet ic 7474 [klik disini]

Tidak ada komentar:

Posting Komentar